“摩爾定律”[1]成功預(yù)測了半導(dǎo)體領(lǐng)域的技術(shù)發(fā)展,然而隨著傳統(tǒng)的硅晶體管的尺寸接近理論極限——柵極長度5納米(低于此極限將產(chǎn)生“短溝道效應(yīng)”,晶體管就會失效),集成電路上元器件數(shù)目的增加速度開始放緩。要知道晶體管的最小尺寸越小,單位面積的芯片(比如電腦和智能手機(jī)上的CPU)就能包括更多晶體管,芯片性能就越強(qiáng)而價格就越便宜。為了打破這一桎梏,科學(xué)家們開始尋找新的材料,試圖代替接近理論極限的“硅”。

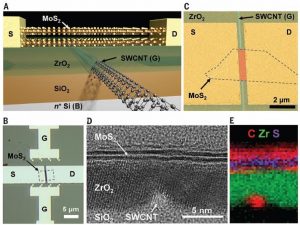

? ? ? ? 近日,加州大學(xué)伯克利分校(UC Berkeley)的Ali Javey教授課題組在Science發(fā)表文章,制備出柵極長度僅有“1納米”的晶體管,這種晶體管采用二硫化鉬(MoS2)材料,使用單壁碳納米管作柵極電極。(MoS2 transistors with 1-nanometer gate lengths. Science, 2016, 354, 99-102, DOI: 10.1126/science.aah4698)

傳統(tǒng)硅(Si)晶體管被認(rèn)為柵極長度不能低于臨界尺寸5nm,否則會出現(xiàn)嚴(yán)重的短溝道效應(yīng),導(dǎo)致源極-漏極間的量子隧穿效應(yīng),電子就能夠“穿過”它面前的“障礙物”從而使得柵極失去靜電調(diào)控能力。因此小于臨界尺寸的晶體管無法處于關(guān)閉狀態(tài),不能形成有效的門電路。

? ? ? ? 想要制備出更小的晶體管,就需要尋找層狀的半導(dǎo)體替代材料,并使其具有更低的介電常數(shù)、較大的帶隙和較重的有效載流子質(zhì)量。研究者選中了單壁碳納米管做柵極電極,源極和漏極之間使用單層MoS2。通過研究過渡金屬硫化物的能帶結(jié)構(gòu),單層或幾層MoS2已被證明優(yōu)于Si材料并且不受其在晶體管中5nm的最低條件限制,其隧穿漏電流比Si小兩個數(shù)量級以上。

通過實驗,器件具有優(yōu)異的開關(guān)特性,開關(guān)電流比約為106,并且其亞閾值搖擺幅度只有65 mV/dec。仿真結(jié)果顯示該晶體管的有效溝道長度在關(guān)閉狀態(tài)時約為3.9納米,打開狀態(tài)時約為1納米。

當(dāng)然,這一研究依然是處于實驗室階段,尚未實現(xiàn)批量生產(chǎn)并轉(zhuǎn)移至實際芯片上。不過,研究者的工作讓突破傳統(tǒng)硅晶體管物理極限變的可能,通過新材料的應(yīng)用,晶體管不會停步在5納米,